### Features

- 3 ns A-B switching

- 300 MHz bandwidth

- Power down mode

- TTL/CMOS compatible controls

- Fixed gain of 1

- 400V/µs slew rate

## Applications

- RGB multiplexing

- Picture-in-picture

- Cable driving

- HDTV processing

- Switched gain amplifiers

- ADC input multiplexer

## **Ordering Information**

| Part No. | Temp. Range    | Package      | Outline# |

|----------|----------------|--------------|----------|

| EL4331CS | -45°C to +85°C | 16-Lead SOIC | MDP0027  |

|          |                |              |          |

## **General Description**

The EL4331C is a triple, very high speed, 2:1 Multiplexing Amplifier. It is intended primarily for component video multiplexing, and is especially suited for pixel switching. The amplifiers have their gain set to 1, internally. All three amplifiers are switched simultaneously from their A to B inputs by the TTL/CMOS compatible, common A/B control pin.

The EL4331C has a power down mode, in which the total supply current drops to less than 1 mA. In this mode, each output will appear as a high impedance.

The EL4331C runs from standard  $\pm 5V$  supplies, and is available in the narrow 16-pin small outline package.

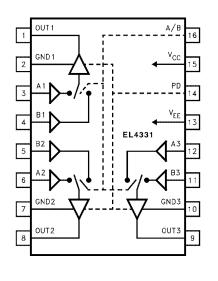

## **Connection Diagrams**

### Absolute Maximum Ratings (T<sub>A</sub> = 25 °C)

| V <sub>CC</sub> to V <sub>EE</sub> |        | 14V                                                                                              | Input Current, Any Input             | 5 mA            |

|------------------------------------|--------|--------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|

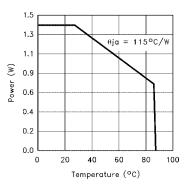

| V <sub>CC</sub> to Any GND         |        | 12V                                                                                              | Power Dissipation                    | See curves      |

| V <sub>EE</sub> to Any GND         |        | 12V                                                                                              | Operating Temperature                | -45°C to +85°C  |

| Continuous Output C                | urrent | 45 mA                                                                                            | Leading Temperature during Soldering | 300°C           |

| Any Input (except PE               | ))     | $V_{\mbox{\scriptsize EE}}\mbox{-}0.3\mbox{V}$ to $V_{\mbox{\scriptsize CC}}\mbox{+}0.3\mbox{V}$ | Junction Temperature                 | 170°C           |

| P <sub>D</sub> Input               |        | V <sub>CC</sub> -7V to V <sub>CC</sub> +0.3V                                                     | Storage Temperature                  | -60°C to +150°C |

|                                    |        |                                                                                                  |                                      |                 |

#### **Important Note:**

All parameters having Min/Max specifications are guaranteed. The Test Level column indicates the specific device testing actually performed during production and Quality inspection. Elantec performs most electrical tests using modern high-speed automatic test equipment, specifically the LTX77 Series system. Unless otherwise noted, all tests are pulsed tests, therefor  $T_J = T_C = T_A$ .

#### Test Level Test Procedure

| I 100% productio | n tested and QA sample | tested per QA test plan QCX00 | 02. |

|------------------|------------------------|-------------------------------|-----|

|------------------|------------------------|-------------------------------|-----|

- II 100% production tested at  $T_A = 25^{\circ}C$  and QA sample tested at  $T_A = 25^{\circ}C$ ,  $T_{MAX}$  and  $T_{MIN}$  per QA test plan QCX0002.

- III QA sample tested per QA test plan QCX0002.

- IV Parameter is guaranteed (but not tested) by Design and Characterization Data.

- V Parameter is typical value at  $T_A = 25^{\circ}C$  for information purposes only.

#### **DC Electrical Characteristics**

$V_{CC}$  = +5V,  $V_{EE}$  = -5V, Ambient Temperature =25°C,  $R_L$  = 500 $\Omega,$   $P_D$  = 5V

| Parameter             | Description                                          | Min  | Тур     | Max  | Test Level | Units |

|-----------------------|------------------------------------------------------|------|---------|------|------------|-------|

| V <sub>OS</sub>       | Input Referred Offset Voltage                        |      | -12     | 30   | П          | mV    |

| dVOS                  | Input A to Input B Offset Voltage [1]                |      | 1       | 8    | II         | mV    |

| IB                    | Input Bias Current                                   |      | -7      | -30  | Π          | μΑ    |

| dI <sub>B</sub>       | Input A to Input B Bias Current [1]                  |      | 0.5     | 4.0  | П          | μΑ    |

| AVOL                  | Open Loop Gain (from Gain Error Calculation)         |      | 54      |      | v          | dB    |

| PSRR                  | Power Supply Rejection Ratio                         | 60   | 70      |      | П          | dB    |

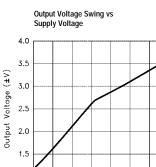

| V <sub>OUT</sub> _500 | Output Voltage Swing into $500\Omega$ Load           | ±2.7 | ±3.2    |      | П          | V     |

| V <sub>OUT</sub> _150 | Output Voltage Swing into 150Ω Load                  |      | +3/-2.7 |      | v          | V     |

| I <sub>OUT</sub>      | Current Output, Measured with 75  load [2]           | 30   | 40      |      | П          | mA    |

| X <sub>TALK</sub>     | Crosstalk from Non-Selected Input (at DC)            | -70  | -85     |      | П          | dB    |

| V <sub>IH</sub>       | Input Logic High Level (A/B and PD)                  | 2.0  |         |      | II         | V     |

| V <sub>IL</sub>       | Input Logic Low Level (A/B and PD)                   |      |         | 0.8  | П          | V     |

| I <sub>IL_AB</sub>    | Logic Low Input Current ( $V_{IN} = 0.8V$ ), A/B Pin | -1   | -20     | -100 | П          | μΑ    |

| I <sub>IH_AB</sub>    | Logic High Input Current (VIN = 2.0V), A/B Pin       | -5   | 0       | 5    | II         | μΑ    |

| I <sub>IL_PD</sub>    | Logic Low Input Current ( $V_{IN} = 0.8V$ ), PD Pin  | -10  | 0       | 10   | П          | μΑ    |

| I <sub>IH_PD</sub>    | Logic High Input Current ( $V_{IN} = 5.0V$ ), PD Pin | 0.5  | 1.0     | 1.6  | II         | mA    |

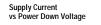

| Is                    | Total Supply Current                                 | 38   | 48      | 60   | II         | mA    |

| I <sub>S(PD)</sub>    | Powered Down Supply Current                          |      | 0.01    | 1.0  | II         | mA    |

1. Any channel's A-input to its B-input.

2. There is no short circuit protection on any output.

## **AC Electrical Characteristics**

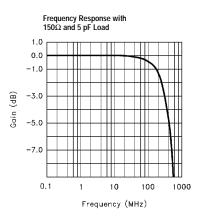

$V_{CC}$  = +5V,  $V_{EE}$  = -0.5V, Ambient Temperature = 25°C,  $R_L$  = 150 $\Omega$  and  $C_L$  = 5 pF

| Parameter                | Description                                  | Min | Тур | Max | Test Level | Units |

|--------------------------|----------------------------------------------|-----|-----|-----|------------|-------|

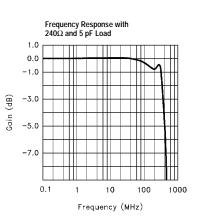

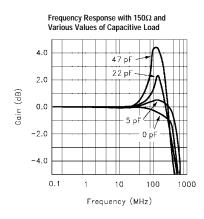

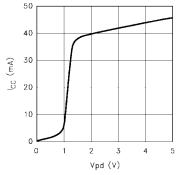

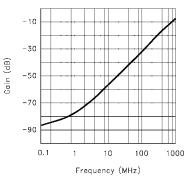

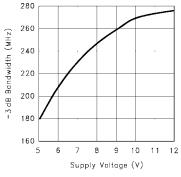

| BW                       | -3 dB Bandwidth                              |     | 300 |     | v          | MHz   |

|                          | -3 dB BW with 250 $\Omega$ and 10 pF Load    |     | 400 |     | v          | MHz   |

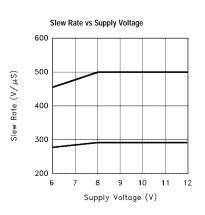

| SR                       | Slew Rate (4V Square Wave, Measured 25%-75%) |     | 400 |     | v          | V/µs  |

| Ts                       | Settling Time to 0.1% of Final Value         |     | 13  |     | v          | ns    |

| T <sub>AB</sub>          | Time to Switch Inputs                        |     | 3   |     | v          | ns    |

| OS                       | Overshoot, $V_{OUT} = 4V_{pk-pk}$            |     | 8   |     | v          | %     |

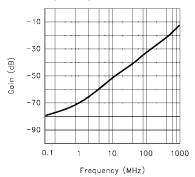

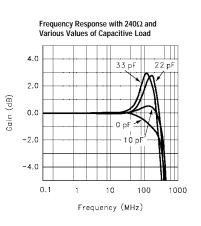

| I <sub>SO-AB</sub> -10M  | Input to Input Isolation at 10 MHz           |     | 53  |     | v          | dB    |

| I <sub>SO-AB</sub> -100M | Input to Input Isolation at 100 MHz          |     | 33  |     | v          | dB    |

| I <sub>SO-CH</sub> -10M  | Channel to Channel Isolation at 10 MHz       |     | 56  |     | v          | dB    |

| Iso-ch-ch-100M           | Channel to Channel Isolation at 100 MHz      |     | 33  |     | v          | dB    |

| Pkg                      | Peaking with Nominal Load                    |     | 0   |     | v          | dB    |

| T <sub>ON_PD</sub>       | Power Down Turn-On Time                      |     | 150 |     | v          | ns    |

| T <sub>OFF_PD</sub>      | Power Down Turn-Off Time                     |     | 1   |     | v          | μs    |

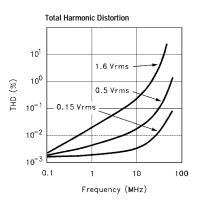

## **Typical Performance Curves**

3 dB Bandwidth Small Signal Transmit Response

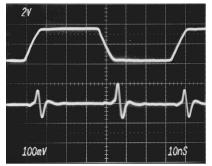

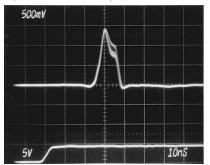

Large Signal Transient Response

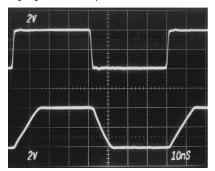

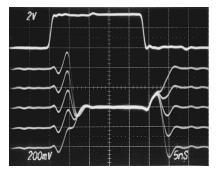

Switching from Ground to An Uncorrelated Sine Wave and Back

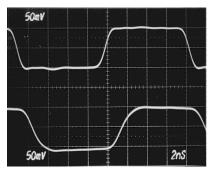

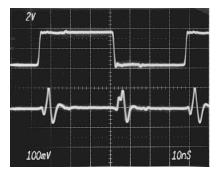

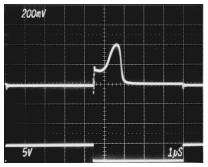

Switching Glitch, OV to OV with 2 ns AB edges

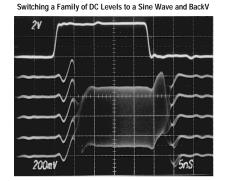

Switching a Family of DC Levels to Ground and Back

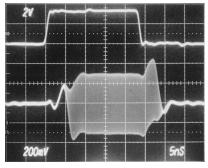

Switching Glitch, OV to OV with 10 ns AB Edges

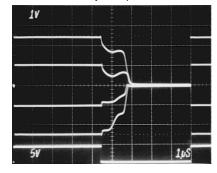

Output Power Down Turn-Off Response

Output Power Down Turn-On Response

A-Input to B-Input Isolation

Channel to Channel Isolation

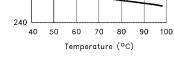

Supply Voltage (V)

1.0

Slew Rate vs Temperature

Siew Rate (V/ $\mu$ S)

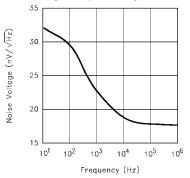

Voltage Noise Spectral Density

### **Applications Information**

#### **Pin Descriptions**

| A1, A2, A3          | "A" inputs to amplifiers 1, 2 and 3 respectively                                                                                                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1, B2, B3          | "B" inputs to amplifiers 1, 2 and 3 respectively                                                                                                                                                                                                            |

| GND1, GND2,<br>GND3 | These are the individual ground pins for each channel.                                                                                                                                                                                                      |

| OUT1, OUT2,<br>OUT3 | Amplifier outputs. Note there is no short circuit protection.                                                                                                                                                                                               |

| V <sub>CC</sub>     | Positive power supply. Typically +5V.                                                                                                                                                                                                                       |

| V <sub>EE</sub>     | Negative power supply, typically -5V.                                                                                                                                                                                                                       |

| A/B                 | Common input select pin, a logic high selects the "A"<br>inputs, logic low selects the "B" inputs. If left to float,<br>this pin will float high and the "A" channels will be<br>selected.                                                                  |

| PD                  | A logic low puts the part into its power down mode. Note<br>that when this pin is at a logic high (+5V), it will sink<br>typically 1 mA. When pulled low, it will source a few<br>$\mu$ A, typically < 25 $\mu$ A. This pin should not be left<br>floating. |

## **Circuit Operation**

Each multiplexing amplifier has two input stages. The multiplexing amplifiers switch from their "A" inputs to their "B" inputs under control of the common **A/B** select pin. The switching has a make before break action. Each amplifier is internally connected for unity gain, allowing larger switching matrixes to be built up. Note however, that each amplifier likes to see a load of  $250\Omega$  or less; load resistances higher than this, can lead to excessive peaking. Load capacitance should be kept down below 40 pF, and 40 pF requires a load resistance of  $\delta$  150 $\Omega$  to keep the output from excessive peaking. Higher capacitive loads can best be driven using a series resistor to isolate the amplifier from the reactive load.

The ground pins are used as a reference for the logic controls. Both **A/B** and **PD** are referenced to ground.

The supplies do not have to be symmetrical around ground, but the logic inputs are referred to the ground pins, and the logic swing must not exceed the +V supply. Due to the fact that all three channels share common control pins, the three grounds **have** to be at the same potential. One third of the 1 mA that **PD** will sink (at 5V) will be seen at each ground pin. Also, the individual grounds are internally connected to their channel compensation capacitor in an effort to keep crosstalk low.

#### A/B Switching

Referring to the photographs showing the 0V–0V switching glitches, it will be noted that slower edges on the A/B control pin result in switching glitches of somewhat less total energy. The switching action is a makebefore-break, so the two inputs essentially get mixed at the output for a few nanoseconds. Note that the two inputs are buffered, so there is no component of one input injected into the other input. The input impedance does not depend on whether an input has been selected.

#### **Power Down**

Referring to the photographs of the power down function and Figure 4, it will be noted that there is a considerable glitch in the output as the part powers down. It will also be noted that the power down time is considerably longer than power up, 1  $\mu$ s compared to 150 ns. In power down mode, the whole amplifier, its reference and bias lines are all powered down. At the same time, the output stage has been configured so that the powered down output appears as a high impedance. This allows circuits such as the multiplexer shown in application #4 to be realized, although the price is the

Triple 2:1 Mux-Amp AV = 1

*EL4331C*

significant output disturbance as one part turns on before the other has fully turned off. V<sub>CC</sub> A/B SELECT A/B R 1 RO Δ G 1 B1 GO EL 4 3 3 1 А R2 G2 B0 EL4331 B2

Figure 1. Two RGB Sources Multiplexed to One RGB Output

#### **Single Supply Operation**

Due to the fact that video signals often have negative sync levels and invariably require ground to be within the signal swing, running the EL4331 on a single supply rail compromises many aspects of its performance. It is difficult to generate a solid, clean, pseudo ground a few volts away from ground without using more power, and components than simply providing a negative power rail. A signal ground has to be capable of handling all the return currents from all the inputs, as well as the outputs, from DC to frequencies in excess of 400 MHz. While this is by no means impossible, a negative rail can be generated from a standard +5V rail for a couple of dollars and a square inch, or less, of board space. However, a pseudo ground can be derived with for example an LM336, to give an "AC ground" 2.5V above 0V. The logic inputs will need some form of level shifting to ensure that the logic "1" and "0" specifications can be met. The pseudo ground must be well bypassed to the real ground; note that the pseudo ground will have to sink/source all the current that flows in the internal compensation capacitors during slewing. This can easily be several milliamps in a few nanoseconds. If the pseudo ground "moves" because one channel is forcing current into the derived ground, cross-talk into the other two channels will become very significant.

#### **Application Circuit #1**

Figure 1 shows a very high speed RGB (or YUV) multiplexer. Two video sources can be displayed on one monitor with the only stipulation that the video sources have to be synchronous. An example is a picture-in-picture, or "window" is generated with one video source (e.g. RGB TV) in a window, and a computer application around it. Multiplexing synchronous RGB signals has the advantage that the video signals do not have to be digitized, and an image stored in RAM prior to being displayed.

When the monitor is switched off, or goes into its power-saving blanked mode, the EL4331 can be powered down to further save power. The input impedance does not change appreciably between powered up and down modes, although the bias current does drop to near zero.

A demonstration board with this circuit on it is available from Elantec.

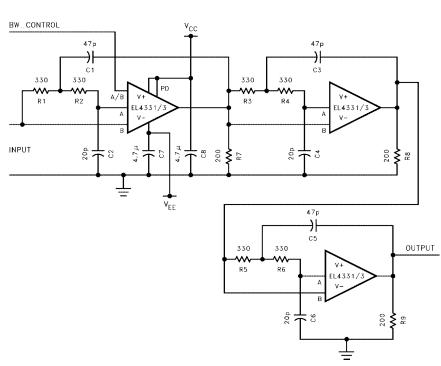

Figure 2. A Bandwidth-Selectable Filter

#### **Application Circuit #2**

Figure 2 shows a circuit that has either a very wide bandwidth, or an 11 MHz low pass response. The EL4331's "A" inputs are connected to the one frequency determining set of components, while the "B" inputs are connected directly. The A/B select pin therefore selects the desired bandwidth. This would allow appropriate filtering to clean up noisy low bandwidth video signals when displaying them on a high quality wide bandwidth monitor.

#### Application Circuit #3

Figure 3 shows one of the three channels of a component video, 8:1 multiplexer. The A/B select pins naturally allow binary coded addressing—allowing simple micro-processor or state machine control. Note that each

amplifier output is loaded, to keep the amplifier outputs damped.

Photograph A1 shows a staircase generated by having all the inputs (sig0 through sig7) connected to a resistive divider chain, and the select bits were driven by a binary counter. Photograph A2 shows the glitch between steps 4 and 5; this is the worst glitch since all three banks of EL4331s are switching together. The magnitude of this glitch is affected by the timing skew of the select lines, the physical length of the traces, and the difference in amplitude of the two signals. This particular circuit was bread-boarded using EL4331s on their adapter boards (available from Elantec for those who can not breadboard with SOICs), and the binary counter was an LS163.

Triple 2:1 Mux-Amp AV = 1

*EL4331C*

## **Applications Information**

| High Speed 8-to-1 Multiplexer                        | Channel Selection Table     |  |  |

|------------------------------------------------------|-----------------------------|--|--|

| Note: No supply bypass capacitors shown and only one | BIT2BIT1BIT0OUTPUT          |  |  |

| of three channels shown.                             | 000SIG0                     |  |  |

| Channel Selection Table                              | 001SIG1                     |  |  |

| BIT2BIT1BIT0OUTPUT                                   | 010SIG2                     |  |  |

| 000SIG0                                              | 011SIG3                     |  |  |

| 001SIG1                                              | 100SIG4                     |  |  |

| 010SIG2                                              | 101SIG5                     |  |  |

| 011SIG3                                              | 110SIG6                     |  |  |

| 100SIG4                                              | 111SIG7                     |  |  |

| 101SIG5                                              | Figure 4. A Simple 8:1 Co   |  |  |

| 110SIG6                                              | Figure 4 shows one of the t |  |  |

|                                                      |                             |  |  |

111SIG7

Figure 3. A High Speed, 8:1 Component Video Multiplexer

Photograph A3 shows the same circuit, with the counter running at 25 MHz. This turns out to be close to the limit of the TTL counter used in the breadboard, rather than the limit of the EL4331. Here the different glitches are easily recognizable-a small glitch for one of the 4 input

EL4331s A/B switching, somewhat larger glitches when two banks switch together, and the biggest glitch when all three banks switch. Photograph A4 shows the big glitch in detail. A good PCB and equal length and matched traces would clean up these glitches.

433129 A1 433130 A2 433131 A3 433132 A4 8-to-1 Multiplexer using Power Down Note: No supply bypass capacitors shown. Only one of three channels shown.

le 8:1 Component Video Multiplexer e of the three channels of a component video, 8:1 multiplexer. In this example, the power down capability is used to save on EL4331s, but as can be seen, the control part does become more complicated. Using the power down mode for multiplexing does, of course, slow down the speed with which one can select a

given input channel. However, if input channel selection can be done during a blanking period, the couple of microseconds that it takes to power down one

chip may be no problem. Note that some external logic is needed in this application, both to select the appropriate amplifier, and also to force a break-before-make action by pulling the T\_OFF line low. All this logic would best be incorporated inside a PAL or gate array, and is shown in gate form just to illustrate the idea. Note that the BIT0 line would have the 3 ns response time, since it is switching the muxamps directly.

Photograph B1 shows a staircase generated by having all the inputs (sig0 through sig7) connected to a resistive divider chain, and then the select bits and the PD pins were driven by a binary counter and a 2-line to 1 of 4 decoder. Photograph B2 shows the glitch between steps 4 and 5; this glitch is caused by the fact that the amplifier that has just been powered up momentarily fights the amplifier that has been powered down, but is not yet off. As seen in the photograph, this causes a glitch of about 200 ns duration. However, when the A/B select pin changes inputs, the glitches are much smaller, as shown in photograph B3. Photograph B4 shows the +2.5V to

-2.5V transition. This is another PD caused glitch, similar to the step 4 to step 5 glitch, but with a much increased magnitude—which causes significantly more fighting between the output stages.

Despite the glitches, if the PD switching can be done during signal blanking, and only A/B switching is used

during the picture, this simple multiplexer has significant parts savings and power savings when compared to the high performance multiplexer in the previous application note.

Elantec, Inc.

**General Disclaimer**

1996 Tarob Court Milpitas, CA 95035 Telephone: (408) 945-1323 (800) 333-6314 Fax: (408) 945-9305 European Office: 44-71-482-4596

HIGH PERFORMANCE ANALOG INTEGRATED CIRCUITS

herein and makes no representations that they are free from patent infringement.

#### WARNING - Life Support Policy

Elantec, Inc. products are not authorized for and should not be used within Life Support Systems without the specific written consent of Elantec, Inc. Life Support systems are equipment intended to support or sustain life and whose failure to perform when properly used in accordance with instructions provided can be reasonably expected to result in significant personal injury or death. Users contemplating application of Elantec, Inc. Products in Life Support Systems are requested to contact Elantec, Inc. factory headquarters to establish suitable terms & conditions for these applications. Elantec, Inc.'s warranty is limited to replacement of defective components and does not cover injury to persons or property or other consequential damages.

Specifications contained in this data sheet are in effect as of the publication date shown. Elantec, Inc. reserves the right to make changes in the circuitry or specifications contained herein at any time without notice. Elantec, Inc. assumes no responsibility for the use of any circuits described